با دسترسی محدود به تراشههای پیشرفته جدید به دلیل محدودیتهای اعمال شده توسط ایالات متحده، دانشمندان در چین مجبور شدهاند در هنگام توسعه فناوریهایی مانند ابررایانهها و هوش مصنوعی (AI) خارج از چارچوب فکر کنند. آخرین نوآوری آنها یک پردازنده است – نسخه اولیه آن “ژجیانگ” نام دارد – که توسط تیمی از موسسه فناوری محاسباتی (ICT)، آکادمی علوم چین، توسعه یافته است و جزئیات کار آنها در مقالهای در ژورنال معتبر تحقیقاتی بنیادی در ۲۹ دسامبر ارائه شد.

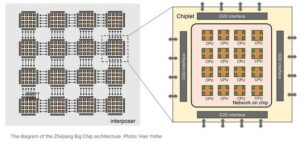

ژجیانگ مساحتی به اندازه هزاران میلی متر مربع را پوشش میدهد و از ۱۶ چیپلت با ۲۵۶ هسته تشکیل شده است. به گفته محققان این تراشه میتواند تا ۱۰۰ چیپلت، معادل ۱۶۰۰ هسته در مجموع را مقیاسبندی کند.

این تراشه میتواند در محاسبات با کارایی بالا (HPC) استفاده شود و آموزش هوش مصنوعی نسل بعدی را تقویت کند.

با پایان یافتن قانون مور (قانون مور، قاعدهای است که بیان میکند تعداد ترانزیستورهای روی یک تراشه با مساحت ثابت هر ۲ سال، بهطور تقریبی دو برابر میشود)، اجرای تراشههای با کارایی بالا از طریق مقیاسبندی ترانزیستور به طور فزایندهای چالش برانگیز شده است. برای بهبود عملکرد، افزایش سطح تراشه برای ادغام ترانزیستورهای بیشتر به یک رویکرد ضروری تبدیل شده است.

برای طراحی تراشهای با مساحت بزرگتر – چیزی که محدودیتهای هزینه، بازده و فناوری لیتوگرافی را میشکند – تیم یک شکل تراشه جدید را پیشنهاد کرد که نام آن را “تراشه بزرگ” (Big Chip) گذاشتند.

تراشه بزرگ، به تراشهای اطلاق میشود که بزرگتر از محدوده مساحت پیشرفتهترین دستگاه لیتوگرافی موجود است و دو ویژگی اصلی دارد. اول، تراشه واقعا بزرگ است. به دلیل اندازه آن، میتواند قطعات الکترونیکی یا ترانزیستورهای ریزتری نسبت به یک تراشه تک تکه معمولی ساخته شده با فناوری موجود داشته باشد.

دوم، تراشه بزرگ دارای چندین قالب کاربردی است و از چند تکنیک ساخت نیمه هادی در حال ظهور برای ادغام قالبهای پیش ساخته در این تراشه استفاده میشود.

تراشه بزرگ که از بیش از یک تریلیون ترانزیستور تشکیل شده، میتواند با استفاده از دو رویکرد ایجاد شود. اولین رویکرد یکپارچه سازی چیپلت است که شامل ترکیب چند تراشه بر روی یک بستر در یک بسته واحد است. SoC Kunpeng 920 هوآوی (سیستم روی یک تراشه) نمونه خوبی است که در آن اندازه یک CPU معمولی دارد.

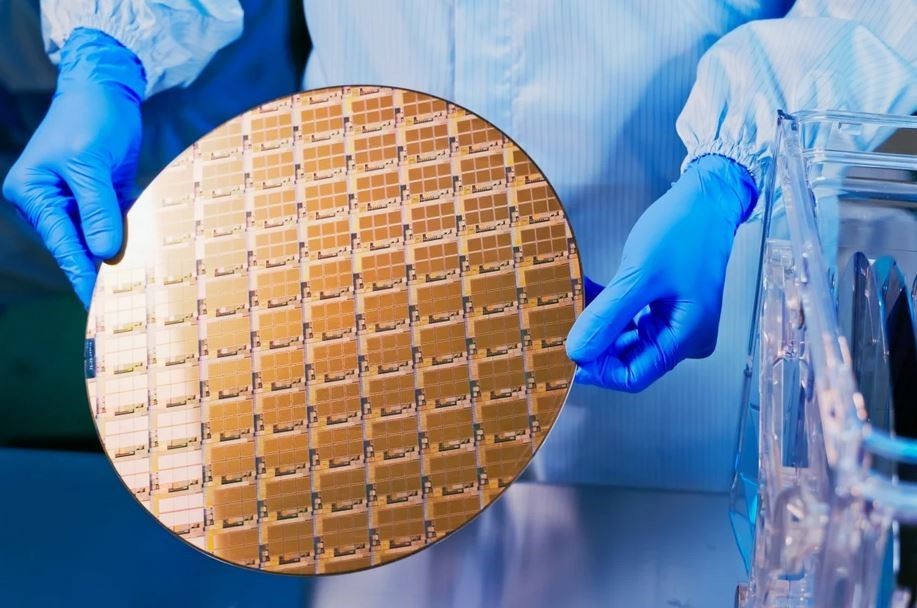

رویکرد دوم یکپارچه سازی در مقیاس ویفر (WSI) است که شامل ساخت یک مدار مجتمع بسیار بزرگ از یک ویفر سیلیکونی کامل است.

با WSI، پردازنده تراشه بزرگ ژجیانگ بر روی یک فرآیند CMOS 22 نانومتری طراحی و ساخته شده است.

از آنجایی که تراشههای بزرگ حاوی هستههای بیشتری هستند، ارتباط بین هستهها بر همکاری آنها تأثیر میگذارد، بنابراین طراحی معماری تراشهها تأثیر قابل توجهی بر عملکرد دارد.

البته تراشههای بزرگ بدون چالش نیستند. در حالی که آنها میتوانند به یک توانایی محاسباتی قدرتمند دست یابند، هنوز با مشکلات کارایی، خنک کننده و عملکرد مواجه هستند.

ساخت تراشههای بزرگ پیچیده است و به دلیل بسیاری از عوامل تاثیرگذار، همیشه انجام آن به طور کامل دشوار است. در حالی که راههایی برای بهبود این امر وجود دارد، اما ممکن است پرهزینه باشد.

تراشههای بزرگ گرمای زیادی ایجاد میکنند، بنابراین داشتن سیستمهای خنککننده مناسب و طراحیهایی که انرژی کمتری مصرف میکنند بسیار مهم است. نقشه برداری کار و اکتشاف فضای طراحی در طراحی تراشه بزرگ نیز برای اجرا چالش برانگیز است.

منبع: scmp